## Mestrado integrado e Licenciatura em Engenharia Informática

Disciplina de Sistemas Lógicos – 2º teste (recurso) – 18/01/2014

Duração: 1h20mn | Tolerância: 10mn | Sem consulta

Importante: numere as folhas que entregar (ex. 1 de 4) e identifique-se em todas elas

## Responda em folhas separadas aos dois grupos de questões

## Q1 (3 + 3 + 4 valores)

a) Utilizando um flip-flop do tipo D, <u>apresente,</u> <u>justificando</u>, <u>o circuito necessário para</u> <u>obter um flip-flop do tipo T</u>.

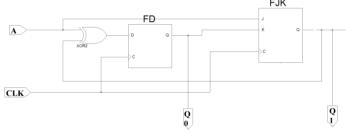

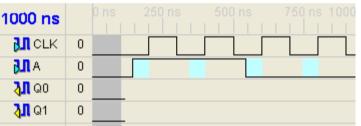

b) Considere o circuito sequencial síncrono representado pelo esquemático (ao lado). A partir do estado inicial Q1=0 e Q0=0, complete o diagrama temporal em relação a Q1 e Q0 segundo a variação das entrada 'A' e CLK (Clock) representada. Utilize a folha de resposta e não o enunciado para apresentar a sua resposta.

c) Pretende-se desenvolver um sistema para detectar a presença de uma sequência de dois bits seguidos iguais (iguais a zero ou iguais a um) numa entrada série binária X. A saída Z deve tomar o valor 1 quando a sequência é detectada. Considere que são de considerar sobreposições entre sequências válidas (isto é, a saída de uma sequência pode contribuir para a sequência seguinte). Apresente um diagrama de estados para o detector de sequência.

## Q2 (3 + 4 + 3 valores)

Pretende-se projetar um contador síncrono de 3 bits, com RESET síncrono, que contará em módulo 6, utilizando os estados de contagem 0, 4, 2, 1, 3 e 6 (em binário natural, e por esta ordem), sendo o estado 0 o estado inicial de contagem. A entrada RESET controla o modo funcionamento do contador: quando RESET=0 o circuito conta de forma ascendente segundo a ordem atrás especificada; quando RESET=1 o contador segue para o estado inicial de contagem. Nota: As saídas coincidem com as variáveis de estado.

- a) <u>Apresente tabela de transição de estados codificados do contador</u>. IMPORTANTE: Considere como *don't care* as situações não previstas na especificação do contador!

- b) Utilizando flip-flops D, <u>apresente as tabelas das entradas D<sub>2</sub>, D<sub>1</sub> e D<sub>0</sub>, mapas de Karnaugh associados e expressões simplificadas</u> (não é necessário apresentar o esquema lógico). IMPORTANTE: Considere como *don't care* as situações não previstas na especificação do contador!

- c) Considere que o contador arranca no estado com todas as variáveis de estado a 1 (devido a mau funcionamento). <u>Indique os estados seguintes quando RESET=0 e quando RESET=1 resultantes da solução apresentada na alínea anterior</u>. <u>Justifique a resposta</u>.