Departamento de Engenharia Electrotécnica

## Licenciatura em Eng. Informática

Disciplina de Sistemas Lógicos – Exame Época Recurso – 3/2/2011 Duração: 1h50mn Tolerância: 10mn Sem consulta

Importante: numere as folhas que entregar (ex. 1 de 4) e identifique-se em todas elas Responda em folhas separadas aos vários grupos de questões

## Q1 (2.5 + 2.5 + 2.5 valores)

- a) Considere que a função  $f(A,B,C,D) = \sum (0,2,4,8,10,12) + d(6,13)$ . Obtenha uma expressão simplificada na forma de soma de produtos através do método de Quine McCluskey.

- b) Implemente a função  $f(A,B,C,D) = \sum (0,2,4,8,10,12)$  utilizando descodificadores de dois bits de entrada e lógica adicional que considere conveniente. Tente utilizar o menor número de descodificadores. Justifique a resposta.

- c) Pretende-se realizar um bloco que implemente a expressão **aritmética** a\*b-2\*c, em que a, b e c são números de um bit cada, "\*" é a operação aritmética de multiplicação e "-" representa a operação aritmética de subtracção. Determine o número de bits necessários para representar a saída em complemento para 2 e apresente a tabela de verdade associada.

## Q2 (1.5 + 3.5 + 2 valores)

Pretende-se projectar um contador síncrono, com 3 bits, que contará em módulo 6, utilizando os estados de contagem 0, 6, 1, 5, 2 e 4 (em decimal), sendo o estado 0 o estado inicial de contagem. Nota: As saídas coincidem com as variáveis de estado.

- a) Apresente tabela de transição de estados e codificação de estados proposta.

- b) Utilizando um flip-flop D para o bit mais significativo, outro do tipo T para o segundo bit e outro do tipo JK para o bit menos significativo, apresente as tabelas das entradas D, T, J e K, mapas de Karnaugh associados e expressões simplificadas (não é necessário apresentar o esquema lógico).

- c) Diga qual o estado seguinte do circuito (após um *clock*) quando os flip-flops estiverem a 1 (por exemplo após a alimentação).

## Q3 (3 + 2.5 valores)

- a) Pretende-se desenvolver um sistema para detectar a sequência 01<sup>+</sup>00 presente numa entrada X, em que 1<sup>+</sup> significa uma ou mais ocorrências do símbolo 1. A saída Z deve tomar o valor 1 quando a sequência é detectada. Considere que são de considerar sobreposições entra sequências válidas (isto é, a saída de uma sequência pode contribuir para a sequência seguinte). Apresente um diagrama de estados para o detector de sequência.

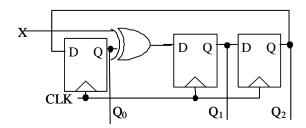

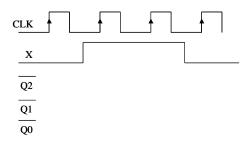

- b) Considere o circuito sequencial síncrono representado na figura. Considerando o estado inicial Q2Q1Q0 = 111, complete o seguinte diagrama temporal.